# LatticeXP2™ Brevia Development Kit

This document provides a brief introduction and instructions to install and run the LatticeXP2 Brevia Development Kit on Windows 7/Vista/XP and select Linux versions. Please refer to the complete documentation at <a href="https://www.latticesemi.com/latticexp2-brevia">www.latticesemi.com/latticexp2-brevia</a>.

# 1

#### Check Kit Contents

The LatticeXP2 Brevia Development Kit contains the following items:

- LatticeXP2 Brevia Evaluation Board pre-loaded with a System-on-Chip (SoC) Demo

- · Parallel connector JTAG cable

- RS232 DB9 null modem cable

- · AC adapter

- · QuickSTART Guide

Static electricity can shorten the lifespan of electronic components. Please handle the kit components carefully.

# 2

#### Connect the LatticeXP2 Brevia Evaluation Board to Your PC

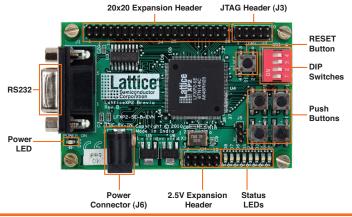

In this step, connect the evaluation board to your PC using the DB9 RS232 cable provided.

- Set all DIP switches (SW1) to the "off" position. This ties the FPGA inputs to 3.3V through pullup resistors (i.e. '1').

- Connect the RS232 cable from the serial port on your PC to the board's RS-232 socket on the left side of the board as shown below.

- 3. Plug in the AC-to-DC converter, and insert the coaxial plug into connector J6.

- 4. After power is applied to the board the red power LED D10 will illuminate.

## LatticeXP2 Brevia Development Kit

Set Up a

### Set Up a Terminal Emulation Program

A terminal emulation program is required to communicate with the evaluation board. Configure your ANSI terminal emulator to communicate over your RS232. Select the following port settings and click **OK**.

- Bits per second: 115200

- Data bits: 8

- · Parity: None

- Stop bits: 1

- Flow control: None

#### Run the System-on-Chip Demo

The LatticeXP2 Brevia Evaluation Board and your computer are now configured. Press the **Reset** button on the board. The factory-configured demo code runs and displays the following banner:

\_\_\_\_\_\_

Welcome to the LatticeXP2 Brevia Development Kit

SoC Demonstration Rev 1.0, April 2010

Main Menu

\_\_\_\_\_\_

- 0: Re-display Main Menu

- 1: Read SPI Flash Memory IDCode

- 2: Read DIP Switch Bank

- 3: Read Data History from SRAM

- 4: Copy Data History from SRAM to SPI Flash Memory

- 5: Read Data History from SPI Flash Memory

- 6: Write Data to SRAM (Specified Address and Data)

- 7: Read Data from SRAM (Specified Address)

- 8: Write Data to SPI (Specified Address and Data)

- 9: Read Data from SPI (Specified Address)

- a: SRAM Auto-Test

- b: SPI Auto-Test

Press 0-b to select an option.

Press 2 on your keyboard to verify the RS232 connection is able to transmit data as well as receive it. You will see this response from the demonstration:

> 2

SW:0x0F

(SRAM Address:0x00006)

#### Run the Reveal Logic Analyzer

- 1. Download the project **Demo\_LatticeXP2\_Brevia\_SoC** from <u>www.latticesemi.com/latticexp2-brevia</u> and extract the files to C:\.

- Connect the JTAG cable between the PC parallel port and J3 on the LatticeXP2 Brevia Evaluation Board. Pins 4, 6, 8 and 10 are not used.

| J3 Pin | Wire Color* | Signal |

|--------|-------------|--------|

| 1      | Violet      | TDO    |

| 2      | Blue        | VCC    |

| 3      | Green       | TDI    |

| 4      | Yellow      | GND    |

| 5      | Orange      | TMS    |

| 6      | Red         | GND    |

| 7      | Brown       | TCK    |

| 8      | _           | GND    |

| 9      | Black       | GND    |

| 10     | _           | GND    |

<sup>\*</sup> If you use a Lattice download cable other than the one in the kit, the colors will be different. Use the signal labels on the wires.

- 3. Start ispLEVER® and open the demo: project\Demo\_LatticeXP2\_Brevia\_SoC.syn.

- 4. Click on the **Logic Analyzer** icon or choose menu item **Tools > Reveal Logic Analyzer**. The Reveal Analyzer tool loads and displays the results from the last successful run.

- 5. Click on the green **Run** button and wait for the red **Stop** button to become available.

- 6. Return to the terminal emulator and select test "b" to run the SPI memory test. The Reveal Analyzer will trigger and display new data.

For more detailed information, download the Reveal Troubleshooting Guide and the Reveal User Guide from the Lattice web site at www.latticesemi.com.

## LatticeXP2 Brevia Development Kit

#### Done!

Congratulations! You have successfully connected and demonstrated the LatticeXP2 Brevia Development Kit. Please refer to the LatticeXP2 Brevia Development Kit User's Guide and the LatticeXP2 Brevia Development Kit web page at <a href="https://www.latticesemi.com/latticexp2-brevia">www.latticesemi.com/latticexp2-brevia</a> for the following:

- · Details on additional evaluation board features and operation

- · Download 28 silicon-proven reference designs

- · Download and install ispLEVER design tools

- · Edit, recompile, and rerun the demo using ispLEVER

- LatticeXP2 Brevia Evaluation Board schematics

#### **Technical Support**

If you experience problems running the kit demos please refer to the Troubleshooting appendix in the LatticeXP2 Brevia Development Kit User's Guide. If problems persist or if any kit contents are missing, please email us at techsupport@latticesmi.com or call 1-800-528-8423 (USA) or +1 503-268-8001 (other locations).

Copyright © 2010 Lattice Semiconductor Corporation. Lattice Semiconductor, L (stylized) Lattice Semiconductor Corp., and Lattice (design), ispLEVER and LatticeXP2 are either registered trademarks or trademarks of Lattice Semiconductor Corporation in the United States and/or other countries. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.